SRAM의 BIST에 대해서 공부하다 찾아본 논문 내용을 정리하고자 한다.

SRAM TEST의 필요성

- 임베디드 sram은 SoC(System-on-Chip)의 큰 비중을 차지하므로, high fault tolerance와 reliability를 가져야 한다.

- 테스트는 메모리의 결함을 분석하고 정확성을 검사하는 필수적인 과정이다.

크게 produciton testing과 field testing으로 나뉜다. - Production testing은 자동 테스트 장비(ATE)를 사용하여 수행되며, 외부 장비를 이용한 테스트이기에 비용이 많이 들고 시간이 오래 걸린다.

- Field Testing은 시스템 내에서 각 임베디드 메모리를 별도로 테스트하는 것이 어렵기 때문에, 내장된 하드웨어 및 소프트웨어를 사용하여 자체적으로 테스트를 수행하는 것이다.

전형적인 SRAM의 아키텍쳐는 다음과 같은 sub block들로 구성되어 있다.

| 구성 요소 (Component) |

설명 (Description) |

| Column Driver | Bitcell Array에서 데이터를 읽고 쓰는 데 필요한 회로를 포함한다. |

| Bitcell Array | 각각 1비트를 저장하는 비트셀로 구성된 2차원 배열. 하나의 비트셀 행(row)은 하나의 워드(word)를 구성한다. |

| Sense Amplifier(SA) | 신호를 증폭하여 선택된 비트셀 행의 데이터를 읽어들이기 위한 아날로그 회로를 포함한다. |

| Address Decoder | 지정된 메모리 주소로부터 워드(비트셀 행)를 디코딩하는 회로이다. |

Fault model과 Test algorithm

BIST의 프로세스는 다음과 같다.

1. March 알고리즘으로 Test pattern 생성

2. Test Controller로 Circuit Under Test(CUT)

3. Output Response Analysis (ORA)

주요 Fault Models

| Fault 종류 (Fault Type) | 설명 (Description) |

| SAF (Struck-at Faults) | 신호가 0 또는 1에 고정되어 변하지 않는 결함 |

| SOF (Stuck Open Faults) | 신호가 열려(Open) 있어서 의도된 동작을 수행하지 못하는 결함 |

| DRF (Data Retention Faults) | 데이터가 메모리에 올바르게 유지되지 않는 결함 |

| AF (Address Fault) | 메모리 주소 접근 오류로 잘못된 워드가 선택되는 결함 |

| ADOF (Address Decoder Open Faults) | 주소 디코더의 연결이 끊어져 주소 해석이 실패하는 결함 |

| TF (Transition Faults) | 신호가 0 → 1 또는 1 → 0으로 정상 전환하지 못하는 결함 |

| CF (Coupling Faults) | 인접 셀 간 간섭으로 인한 결함 (세부 항목 아래 참조) |

| └ CFin (Inversion Coupling Faults) | 한 셀의 상태 변화가 인접 셀의 값을 반전시키는 결함 |

| └ Cfid (Idempotent Coupling Faults) | 인접 셀의 상태를 변화 없이 강제로 고정시키는 결함 |

| └ CFst (State Coupling Faults) | 한 셀의 특정 상태가 인접 셀의 상태를 강제로 설정하는 결함 |

| └ BF (Bridge Coupling Faults) | 두 신호선이 브리지되어 서로 전기적으로 연결되는 결함 |

여러 종류의 Fault Models를 판단하기 위한 다양한 종류의 March Algorithm이 있는데,

알고리즘 종류에 따라 테스트 길이와 판별할 수 있는 Fault 종류 수가 다르기에 적절한 알고리즘 선정이 중요하다.

| Algorithm | Test Length | Fault Coverage |

| March 3 | 10n | AF, SAF, SOF, TF |

| March C | 11n | SAF, TF, CFin, Cfid, CFst, AF |

| March C- | 10n | AF, SAF, TF, CFin, Cfid, CFst |

| March C+ | 14n | AF, SAF, TF, SOF, CFin, Cfid |

| March SS | 22n | SAF, TF, WDF, RDF, DRDF, IRF, CFst, CFds, CFtr, CFwd, CFrd, CFdrd, Cfir |

BUILT-IN SELF TEST(BIST)

- BIST는 DFT(Design for testability)의 일종으로, IC가 자체적으로 기능, 매개변수 등을 검사할 수 있도록 추가 하드웨어와 소프트웨어 기능을 설계하는 기법이다.

- BIST는 외부 자동 시험 장비(ATE)에 대한 의존도를 줄여주며, ET를 더 쉽고 빠르며 효율적이고 비용적으로도 유리하게 만든다.

- BIST의 적용 장점으로는 ATE 의존도 감소, 더 나은 결함 커버리지, 더 짧은 test time, 고객 지원 용이성, 생산 환경 외에서의 시험 가능성이 있다.

- BIST는 Logic BIST(LBIST)와 Memory BIST(MBIST)로 나뉘며, LBIST는 주로 랜덤 논리 시험을 위해 사용되고, MBIST는 메모리 장치를 검사하는 데 사용된다.

- MBIST는 특정한 테스트 패턴을 적용하여 메모리 결함을 드러내는 데 효과적이며, 다양한 산업 표준 알고리즘이 존재한다.(March, Chekerboard 등)

BIST 구성요소

| 구성 요소 | 설명 (Description) |

| BIST Controller |

패턴 생성기(Pattern Generator)와 비교기(Comparator)를 제어한다. 메모리에 대해 Memory BIST Protocol을 준수하며 쓰기 및 읽기 연산을 수행하도록 조정한다. |

| Pattern Generator |

Memory BIST를 위한 다양한 패턴을 생성한다. 생성하는 패턴은 Marching 1s/0s, Alternating 1s/0s, 랜덤 숫자, 고정 패턴 등을 포함한다. |

| Comparator | 메모리에서 읽어온 데이터와 Pattern Generator가 만든 기대 값(expected value)을 비교한다. 일치하지 않는 경우에는 BIST Controller를 통해 실패로 플래그 처리한다. |

BUILT IN SELF REPAIR(BISR)

BISR는 메모리 사용자에게 Access Mode에서 BISR 적용 여부를 선택할 수 있는 유연성을 제공해 주어, 시스템 필요에 따라 리페어 자원 활용 여부를 자유롭게 조정할 수 있다.

- BISR을 적용할 경우(BISR_h = 1) -> 리던던트 워드를 리페어 용도로 활용

- BISR을 적용하지 않을 경우(BISR_h = 0) -> 리던던트 워드를 일반 데이터 워드처럼 활용

<리던던시 자원의 고효율 활용>

BISR을 사용하든 안하든 normal redundant words는 SRAM 내부에 존재하기에 추가면적 증가 없이 높은 활용도를 유지할 수 있다.

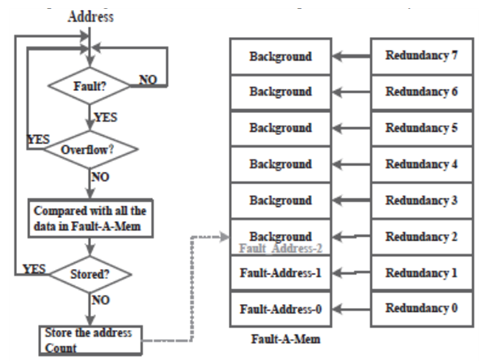

<Fault의 저장 최적화>

같은 결함 주소를 여러 번 저장하지 않고, 오직 한 번만 저장하는 최적화 방법을 적용했다.

실제 저장 방식:

BIST가 fault를 감지하면, BIAA 모듈이 Fault-A-Mem(결함 주소 메모리)에 기록하기 전

이미 저장된 주소들과 비교해 중복 여부를 확인한다.

초기에는 Fault-A-Mem에 "미리 dummy 데이터를 채워놓는 방식" 으로 비교를 단순화하였다.

➔ 결과적으로 메모리 오버헤드를 줄이고 fault 관리 효율을 높였다.

PROPOSED DYNAMIC BISR

Proposed BISR는 회로 내부에 자체 리페어 기능(Built-in Self-Repair)을 두어, Fault 발생 시 외부 개입 없이 스스로 고장 수리를 수행하는 구조를 가진다.

BISR 시스템의 세 가지 핵심 모듈 구성요소:

- BIST (Built-in Self-Test): Fault “탐지” 담당

- BIRA (Built-in Repair Analysis): Fault “분석 및 분류” 담당

- Multiplexer (MUX): 리던던시 적용을 위한 경로 스위칭 담당

BISR의 process는 다음과 같다.

- 먼저 BIST를 통해 메모리 결함(faulty locations)을 검출한다.

- 검출된 Fault는 BIRA를 통해 분석되어 결함 유형 및 개수에 따라 분류된다.

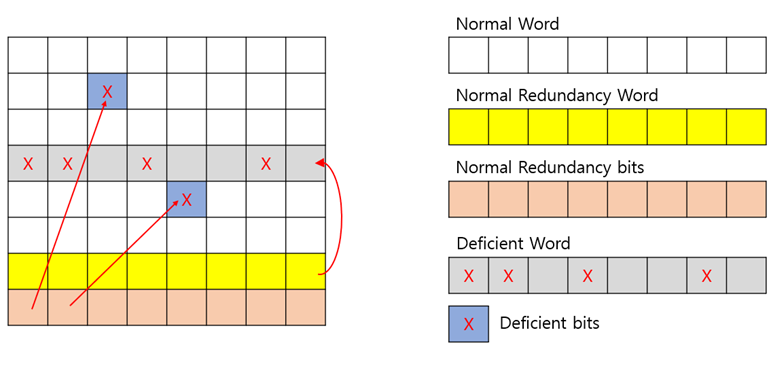

- Fault masking(가리기)은 리던던시 아키텍처를 이용해 수행한다.

- Fault masking 방식:

Address에 많은 Fault가 존재 → 전체 Redundant Word 매핑

Address에 일부 비트만 Fault → 해당 비트만 Redundant Bit로 매핑 - 모든 Faulty Address와 Redundant Address는 1:1 매핑(one-to-one mapping) 되어 수리율(Repair Rate)을 높인다.

Reference

'반도체 > 평가및분석' 카테고리의 다른 글

| 반도체 칩의 불량 분석, Failure Analysis(FA)에 대해서 (eFA, pFA, OFI) (0) | 2025.04.06 |

|---|---|

| [Scan basic] Testability (0) | 2025.03.25 |

| [Scan Basic] 반도체 테스트의 기초 (Fault Model) (0) | 2025.03.21 |