1. 테스트 플로우

테스트 플로우는 다음과 같은 단계로 구성된다:

| 단계 | 설명 |

|---|---|

| Fabrication (FAB) Test | 웨이퍼 수준에서 제조된 칩의 전기적 특성을 테스트합니다. |

| Electrical Die Sorting (EDS) Test | 게이트 수준에서 칩의 기능성을 검증합니다. |

| Assembly Test | 패키징된 칩의 전기적 특성을 평가합니다. |

| Package Test | 패키지된 칩의 기능성을 확인합니다. |

| Module Test | 여러 칩이 모듈로 조립된 시스템의 기능성을 검증합니다. |

| Final Test | 전체 시스템의 기능성과 신뢰성을 검사합니다. |

| Chips on Customer | 최종 제품에 통합될 칩을 고객에게 제공합니다. |

그 중 EDS 테스트의 세부 과정은 다음과 같다.

- ET Test & WBI : 기본적인 전기적 특성 측정(IV측정 등등)

- Hot/Cold Test : 반도체가 고온(80~100)이나 저온(-25~-40) 까지 버틸 수 있는지 3Temp 환경에서 테스트

- Repair/Final Test : defect가 있는 부분을 수정 후 다시 테스트

- Inking : 불량 cell을 특수 잉크로 표시함

불량 cell을 특수 잉크로 표시하는 inking과정은 요즘은 없어지는 inkless 과정으로 바뀌었다고 한다!

2. 결함 유형(Fault Model)

2.1. Permanent Fault : hard defect 등으로 인해 칩에 영구손상이발생

ex) Incorrect connection, missing connection, shorts, opens

2.2. Non-Permanent Fault : 일시적인 손상(에러)

- Soft error: SRAM errors from transient faults(오염, 온도, 파티클, 자기장, 우주선 등)

- Intermittent faults(loose connections, deteriorating or aging components, resistance and capacitance variations)

2.3. Stress condition : non permanent fault가 permanent fault로 바뀜

3. 결함 모델의 필요성

결함 모델은 칩에서 발생할 수 있는 다양한 결함을 시뮬레이션하고 표현하는 데 사용된다.

fault를 사용자들이 컨트롤할수 있는 higher level의 abstraction으로 바꿈.

4. Stuck-at Fault Model(SAF)

- Stuck-at 결함 모델은 가장 널리 사용되는 결함 모델 중 하나이다.

- 로직 값이 항상(permanent) 0이나 1에 고정되어있는 상태이다. (각각 SA0/SA1이라고 한다.)

- 다르게 말하면 항상 Vdd(logic-1)이나 GND(logic-0)에 접촉해있는 상태와 같다.

- 소스-드레인 쇼트나, 디퓨전 오염, metallization 쇼트 등의 physical defect가 원인이다.

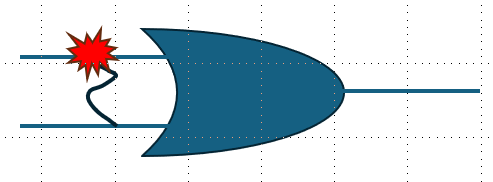

5. Bridging Fault Model

- Bridging 결함 모델은 두 개 이상의 신호 라인이 의도하지 않게 연결되는 결함을 나타낸다.

- 반도체가 미세화 되면서 더욱 중요해지는 fault이며, SAF다음으로 퍼센테이지가 높은 fault이다.

- layout 정보가 필요하다.

6. Delay Fault Model

Delay 결함 모델은 신호의 전달에 딜레이를 유발하는 결함을 시뮬레이션한한다.

- Transition delay fault model : 회로에 오직 하나의 gate에서만 delay가 발생.

0>1, 1>0에서 transition 될 때 Setup/Hold time margin 등의 부족으로 delay 차이 발생(slow-to-rise fault/ slow-to-fall fault) - Gate delay fault model : delay가 발생함에도 전체 성능에 영향을 미치지 않음

- Path-delay fault model : delay들이 조금씩 쌓여 전체 성능에 영향을 미침

7. Stuck-Open Faults(SOF)

- line이 단선됐지만 VDD나 GND에 연결이 되지 않은 상태.

- SAF test에서 탐지되지 않은(설명할 수 없는) defect들을 설명해준다.

- metal line 뿐만 아니라 gate 내의 level(transistor) 내에서도 단선(short) 가능.

'반도체 > 평가및분석' 카테고리의 다른 글

| 반도체 칩의 불량 분석, Failure Analysis(FA)에 대해서 (eFA, pFA, OFI) (0) | 2025.04.06 |

|---|---|

| [Scan basic] Testability (0) | 2025.03.25 |