[MRAM] 뉴메모리 MRAM의 동작 및 역사

뉴메모리의 등장 반도체 소자의 Cell Size가 감소되면서, 여러 문제가 발생하였다. DRAM의 경우 cell이 계속 작아지며 트렌지스터 특성 열화, capacitor 공정 난이도 상승이 일어났고 NAND의 경우 3D 구조

jubrodev.tistory.com

저번 시간에 이어서 MRAM의 동작원리에 대해서 더 자세하게 알아보고자 한다.

MRAM의 동작에 있어 가장 중요한 부분은 TMR이라고 한다. TMR이 커야지 신호차이를 인식하기 좋기 때문이다.

DRAM sense amplifier에 delta Vbl과 같은 느낌이라고 생각하면 된다.

그리고 이 TMR은 온도가 증가할수록 작아진다. sensing에 불리한 것이다.

그래서 고온에서는 이 reading margin을 개선할 필요가 있다.

그러기 위해선 TMR자체를 개선해서 중심값을 개선하거나, 공정 개선으로 산포를 개선하거나, Read 회로를 개선하여 Read 전류를 증가시켜야 한다.

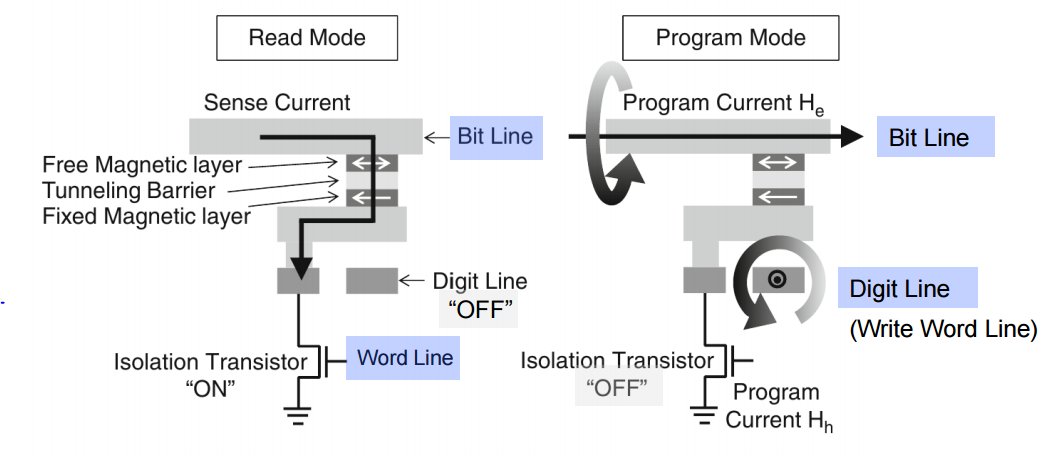

Field Switching MRAM

먼저 Field Switching MRAM의 동작을 살펴보면

1) Read할때는 bit line과 word line 을 on 하여 전류가 흐를 수 있도록 한다.

2) Write할때는 word line을 off 하고 digit line을 on 하여 자화 방향을 바꾸는 작동을 한다.

MRAM은 셀이 인접해있는데, 자기장으로 콘트롤 하기에 주변 셀들도 영향을 받는다. 그래서 x축, y축 두 도선의 자기장을 합쳤을때 유효한 힘이 되어야 write(switching)이 될 수 있도록 한다.

마름모 형태의 그래프를 좀 더 이해하기 위해서,

MTJ 가로 세로 비율이 다를때, 더 긴쪽을 Easy Axis라고 하고, 더 긴쪽으로 정렬되는 것이 에너지적으로 안정된다.

Hard axis field가 없이 Easy axis field힘만 있다면 낮은 에너지> 낮은에너지 이므로 에너지 베리어가 높으니 더 강한 자기장이 필요하다. 마름모 형태 그래프에서 x축 한방향으로 이동하려면 non switching 영역을 벗어나기에 더 큰 힘이 필요한 느낌이다.

결국 Hard axis field가 조금 있으면 더 작은 easy axis field로 switching을 할 수 있다. 그래서 우리가 x,y축 자기장의 합으로 switching을 하는 이유이다.

해결해야 할 과제

1) MTJ size 감소할수록, 단면적이 작아지는 것이므로 똑같은 힘을 주려면 자기장이 세져야 한다.

switching field 증가 > write 전류 증가 > 전력 소모 증가 > 여러 구조들이 다 커져야함 > high density&low cost memory 구현 어려움

2) 공정산포를 고려하면 wirte window가 작아지며 selectivity 열화현상이 일어난다.

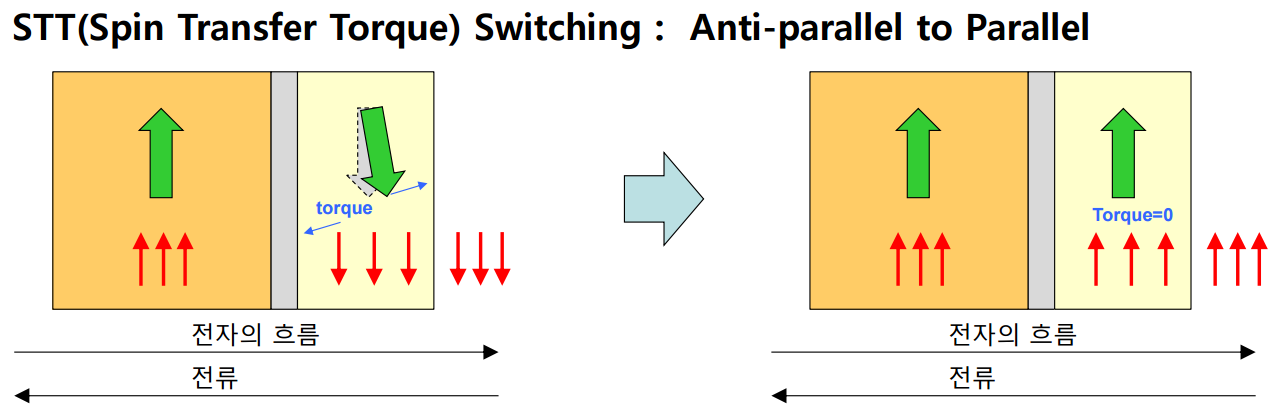

STT-MRAM

STT 방식은 전자의 spin torque를 자화 spin에 전달하며 angular momentum 보존에 의해 자화방향을 바꾸는 방식이라고 저번 글에서 설명했었다.

MRAM wirte하면 자유층을 parallel > anti-parallel , anti-parallel > parallel 로 바꾸는 두가지 경로가 있을것이다.

먼저 anti-parallel > parallel 을 살펴보면

- 전자들이 자유층 Magnetization 방향에 정렬되는 만큼 반작용으로 자유층에 torque 작용

- 전류밀도가 임계 값을 넘으면 자유층의 Magnetization이 고정층의 Magnetization과 평행하게 됨.

parallel > anti-parallel

- 전자들이 자유층에서 고정층으로 갈 때, 고정층 Magnetization과 다른 spin 방향을 가진 소수의 전자

- 들(Minority spin)이 다시 자유층으로 반사됨.

- 반사된 전자들이 자유층에 torque를 가하고, 전류밀도가 임계치를 넘으면 고정층과 같은 방향으로

- switching됨. 고정층은 switching field가 커서 torque를 받아도 switching 되지 않음.

👉AP->P 보다 P-> AP의 전류가 더 많이 든다.(비효율)

Field Switching MRAM:

MTJ size 감소시 switching 전류 증가

STT-MRAM:

MTJ size 감소시 switching 전류 감소

👉STT MRAM이 cell size scaling에 유리!

STT- MRAM Desing시 고려사항

| READ | WRITE | RELIABILITY |

| Read 전류는 sensing을 위해 충분히 커야하는데, 또 너무 크면 read disturb가 발생할 수 있다.(switching이 되어버림) | write전류는 충분히 커야하는데 전류가 커지면 cell transistor도 커야 하기에 chip size 증가, 전력소모 증가의 단점 MTJ write time이 감소하면 write 불량 가능성 증가. 충분한 write time 필요 | 정해진 온도, 시간동안 데이터가 지워지지 않으려면 MTJ Switching을 막기 위한 Energy Barrier는 충분히 높아야 한다 (Data Retention ) 하지만 Energy Barrier가 높으면, MTJ Switching을 위해 큰 전류가 필요하게 되고, 큰 전류로 Write 반복하면 절연막의 Breakdown 유발된다 (MTJ Endurance ). 따라서 MRAM의 동작 수명을 늘리려면 MTJ Switching 전류는 작아져야 한다 |

MRAM의 write margin을 개선하기 위해선 특성 산포를 최소화해야한다.

Write Current 와 Write speed 간의 Trade-off

Write time 감소할 수록 MTJ swiching에 필요한 전류는 증가하는 추세를 보이는데, 10ns 이상에서는 열에너지의 도움으로 switching 전류 감소하고 10ns 이하에서는 열에너지의 기여가 어려워서 switching 전류는 급격히 증가하고, 결국 write시간을10ns 이하로 하는것은 어렵다.

👉write 시간이 짧을수록 필요 전류 증가!

Data retention과 Write성능 trade off

Data retention이 되려면 Energy Barrier가 큰것이 좋은데, Energy Barrier가 크다면 wirte할때 필요 전류가 증가하여 trade off 관계이다.

- 에너지 베리어가 낮을때는, 쉽게 쓸 수 있지만 그만큼 쉽게 없어진다. (모래사장에 글씨쓰기)

- 에너지 베리어가 높을 때는 어렵게 쓸 수 있지만 그만큼 쉽게 없어지지 않는다. (바위에 글자 새기기)

Reference

- T. M. Maffitt et al., "Design Considerations for MRAM" IBM J. Res. & Dev. 50, pp. 25-39 (2006).

- Shinobu Fujita, "MRAM Circuits" in "Handbook of Spintronics", Springer Reference (2016)

- S. Ikeda, IEEE TED 2007

'반도체 공부 > 반도체 제품' 카테고리의 다른 글

| GAAFET 공정 순서 (GAAFET Fabrication Process) (5) | 2025.08.03 |

|---|---|

| [SRAM] 대표적인 메모리 소자인 SRAM 기본 구조 및 동작 이해하기 (0) | 2025.05.12 |

| 모바일 AP 제품(Application Processor, SOC, IP) (0) | 2025.04.02 |

| [PRAM] PRAM의 동작원리 (0) | 2024.11.26 |

| [MRAM] 뉴메모리 MRAM의 동작 및 역사 (1) | 2024.11.08 |