안녕하세요. 한입반도체입니다.

최근 반도체 업계의 올림픽이라 불리는 IEDM 2025에 다녀왔습니다. 이번 Shourt course 중 특히 인상 깊었던 삼성전자 강명길 박사님의 강연, "Limitation and Innovation of transistor technologies" 내용을 바탕으로 차세대 트랜지스터 기술의 흐름과 제 주관적인 분석을 공유해보고자 합니다.

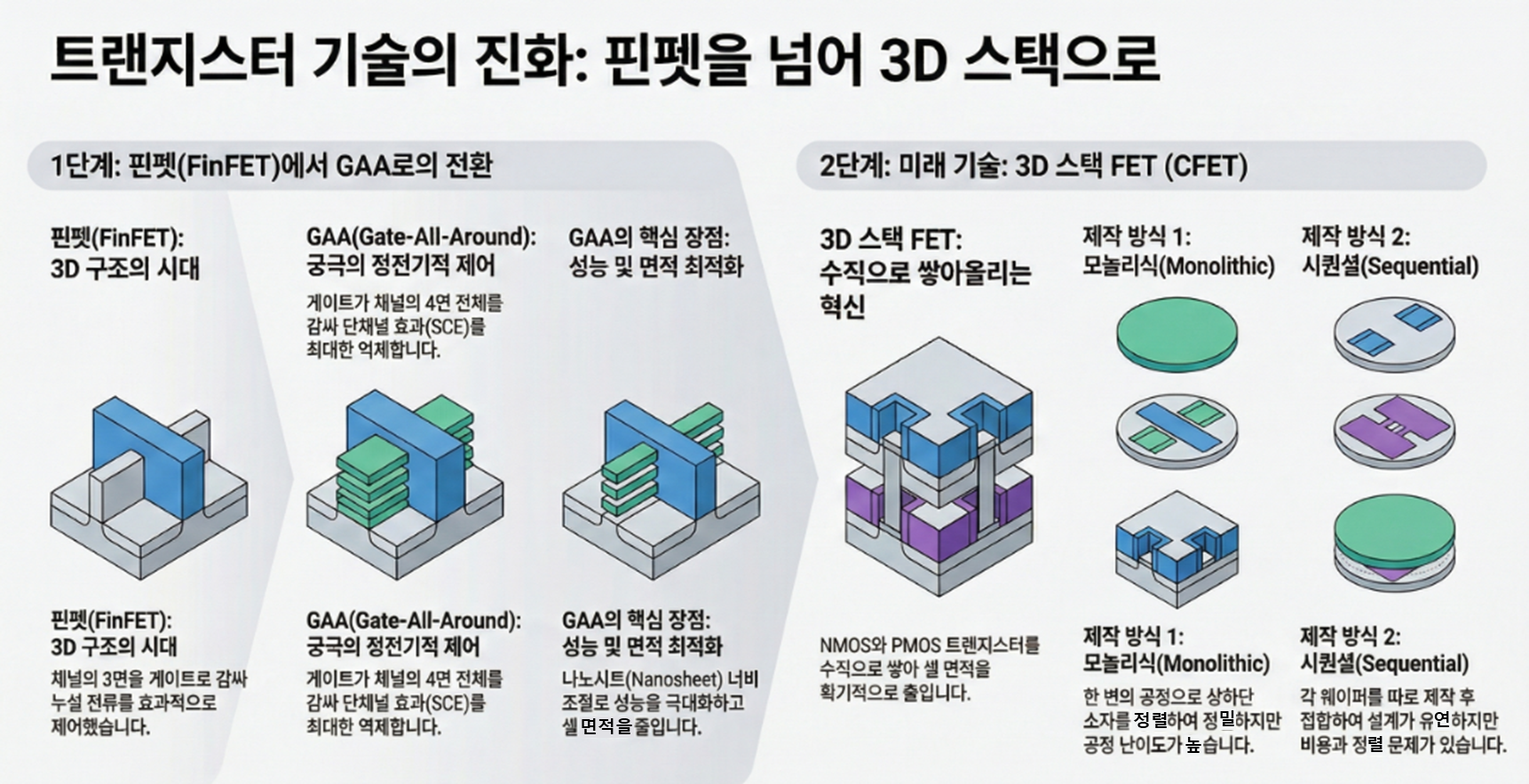

0. 반도체 소자의 발전사

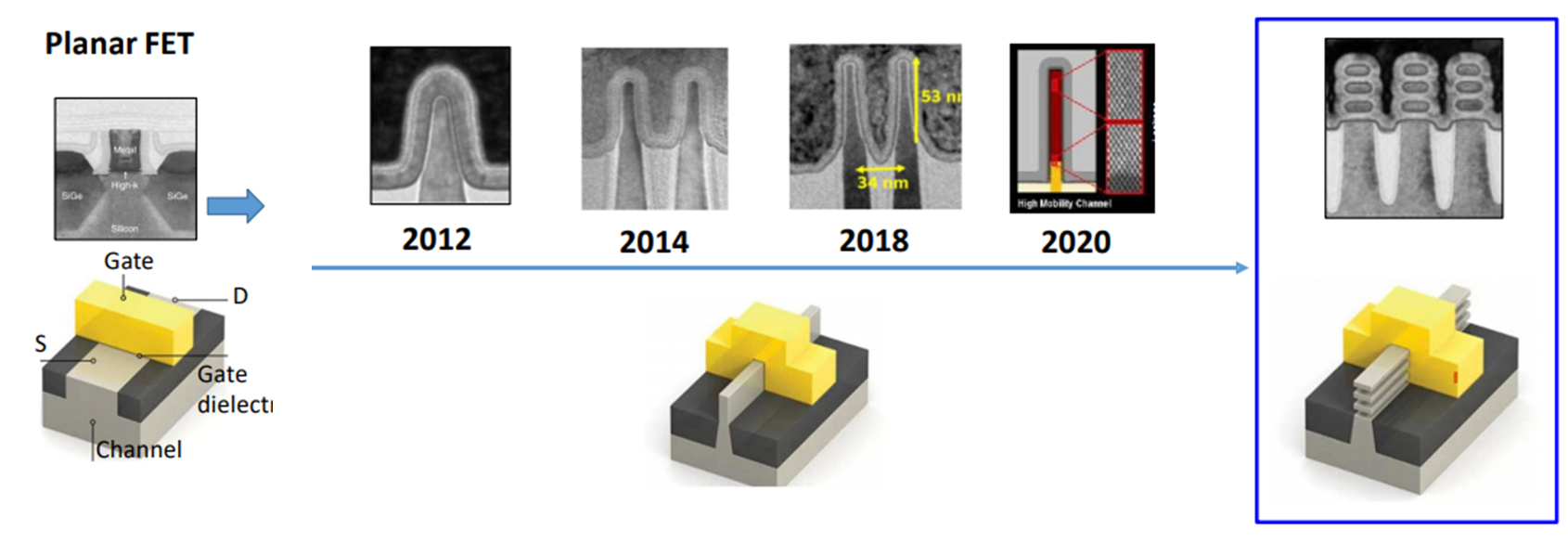

Planar MOSFET

Planar Mosfet에서 Short channel Effect의 한계로, 물리적 scailing의 한계에 봉착하자 90nm 에서는 Stress Engineering(이동도 향상)이, 45nm에서는 HKMG(High-k Metal Gate)가 도입되었습니다. 하지만 구조적 변화 없이는 더 이상의 스케일링이 불가능한 지점에 도달했습니다.

FinFET

2011년경 등장한 FinFET은 반도체 역사의 거대한 변곡점입니다.

- 구조적 특징: 채널을 얇은 지느러미(Fin) 모양으로 세워 게이트가 채널의 3면을 감싸게 했습니다.

- 기술적 이점: 게이트의 지배력이 강화되면서 누설 전류가 획기적으로 줄었고, 동일 면적에서 채널 폭(W_eff)을 확보하여 구동 전류(I_on) 성능을 대폭 끌어올렸습니다.

- 한계: 하지만 3nm 이하로 가면 Fin의 폭을 줄이는 데 한계가 오고, Fin 사이의 간격 때문에 발생하는 기생 커패시턴스 문제가 성능 발목을 잡기 시작했습니다.

https://semiconductor.samsung.com/kr/news-events/tech-blog/gaa-dtco-for-ppa/

삼성전자 Foundry 사업부의 DTCO를 통한 GAA MBCFET™ PPA 최적화 | 삼성반도체

삼성전자 파운드리 사업부는 반도체 학술대회 CICC에서 GAA 트랜지스터를 적용한 3나노 공정의 PPA를 최적화하는 DTCO 활동에 관한 논문을 발표할 예정입니다.

semiconductor.samsung.com

FINFET vs MBCFET의 비교 및 장점은 해당 삼성 뉴스룸에 잘 나와있으니 참고하면 좋을 것 같습니다

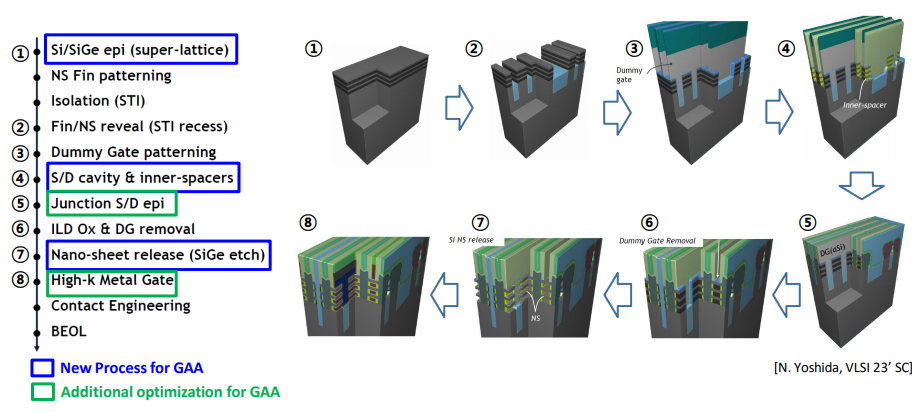

가장 큰 장점은, 기존의 Finfet 소자에서 공정이 그렇게 크게 바뀌지 않는다는 점인 것 같습니다.

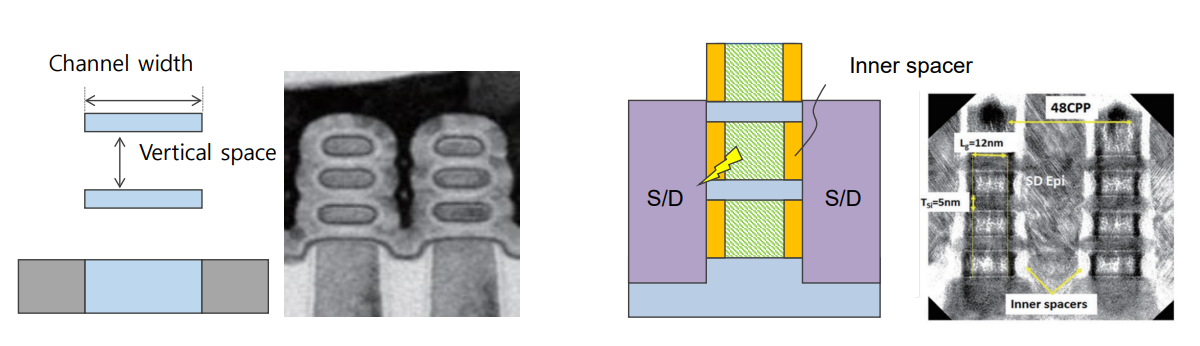

1. GAA (MBCFET™): 구조적 혁신과 '디테일'의 싸움

FinFET은 훌륭한 소자였지만, 미세화가 진행될수록 Cell Height 축소와 양자화된 유효 채널 폭(Weff) 문제가 발목을 잡았습니다. 이를 해결하기 위해 삼성의 독자적인 GAA 구조인 MBCFET™(Multi-Bridge Channel FET)이 도입되었습니다.

FinFET은 핀(Fin) 개수로만 전류를 조절해야 했지만, MBCFET은 나노시트의 폭을 자유롭게 조절하여 고성능(Wide NS)과 저전력(Narrow NS) 설계를 유연하게 최적화할 수 있습니다.

👉하지만 현업 엔지니어로서 주목해야 할 포인트는 'Inner Spacer'와 'Stress Engineering'의 상관관계입니다.

- ● Inner Spacer의 딜레마: 게이트와 소스/드레인(S/D) 사이의 기생 커패시턴스(Parasitic Capacitance)를 줄이기 위해 Inner Spacer는 필수입니다. 하지만 이것이 들어가면 채널(Si/SiGe)의 Epi 성장 품질에 영향을 주어, 채널에 가해져야 할 압축 응력(Compressive Stress)이 완화(Relaxation)되는 부작용이 발생합니다.

- ● 해결책: 결국 Inner Spacer를 적용하면서도 채널 스트레스를 잃지 않는 최적화된 Defective Epi 공정이 소자 성능의 핵심 키가 됩니다.

GAA MBCFET의 기술적 과제 (Challenges in GAA)

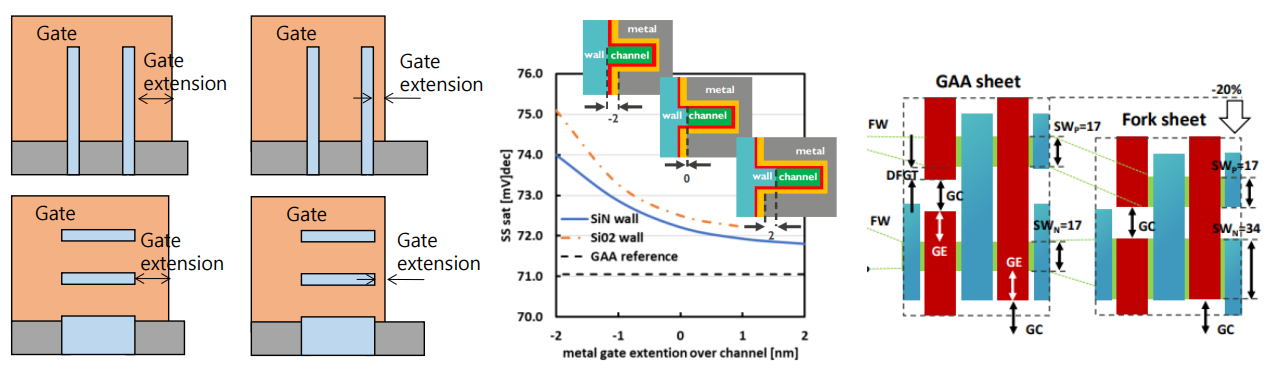

이 외에도 구조적으로 복잡해졌기에, Gate Extension, Bottom channel 등 신경을 써야할 부분이 더 증가했습니다.

Gate Extension의 경우, 위에서 바라보는 Cell Height에 직접적인 영향을 미치기에 집적도에 영향을 주지만, 너무 줄어들면 SS가 증가, 즉 소자의 Controllability가 안좋아지기에 적절한 지점을 찾아야 합니다.

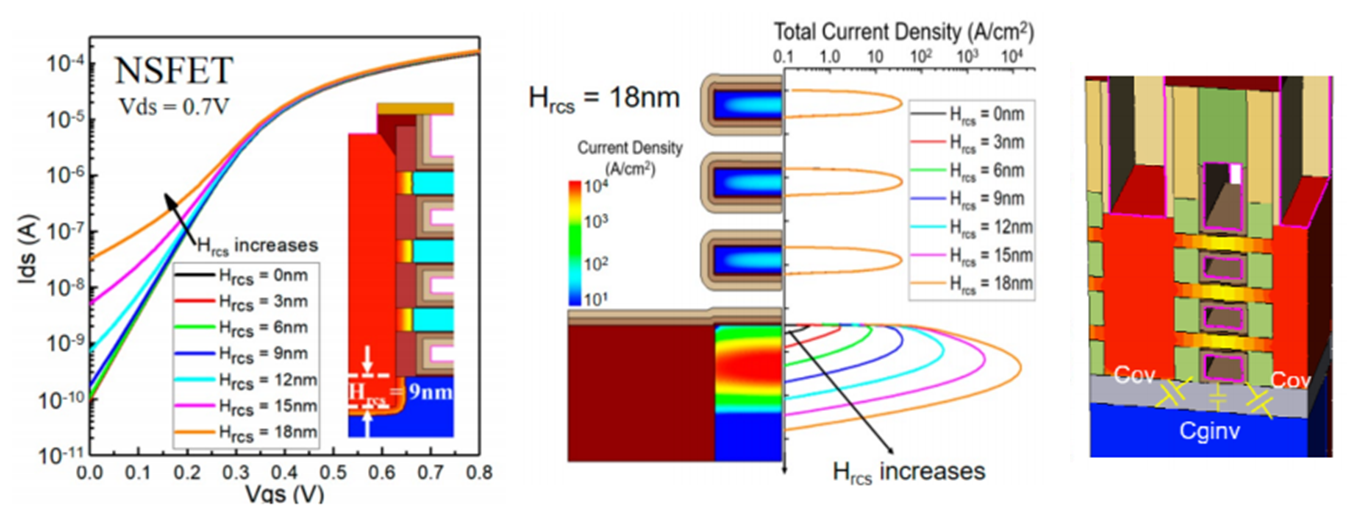

또한, GAAFET의 최하단 채널의 경우, substrate 혹은 Drain Recess 영역과 상호작용을 직접적으로 하며 다른 채널 대비 더 많은 Para Capacity를 유발할 수 있기에 주의해야합니다.

2. Beyond GAA: 3DS-FET (CFET)으로의 진화

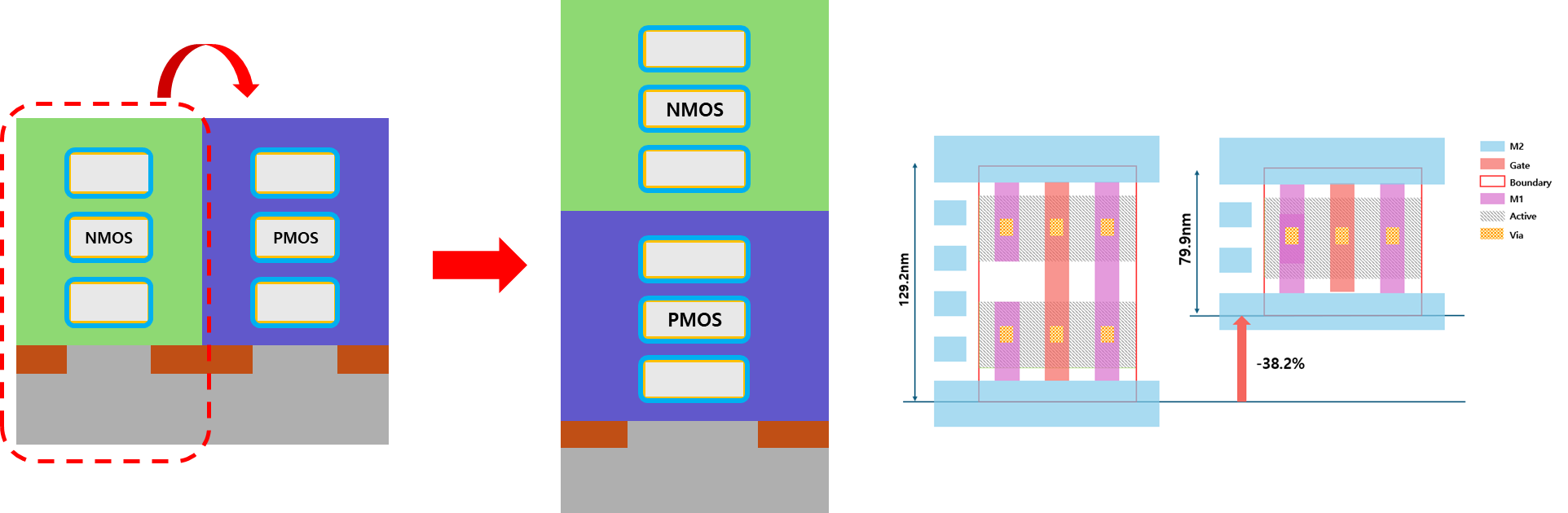

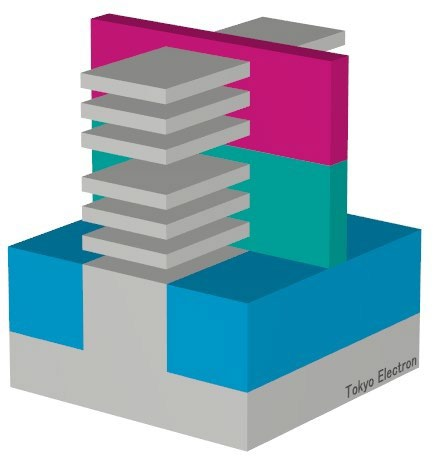

GAA 다음은 무엇일까요? 업계에서는 3DS-FET, 즉 CFET(Complementary FET)을 지목합니다. NMOS와 PMOS를 수직으로 적층(Stacking)하여 면적을 획기적으로 줄이는 기술입니다.

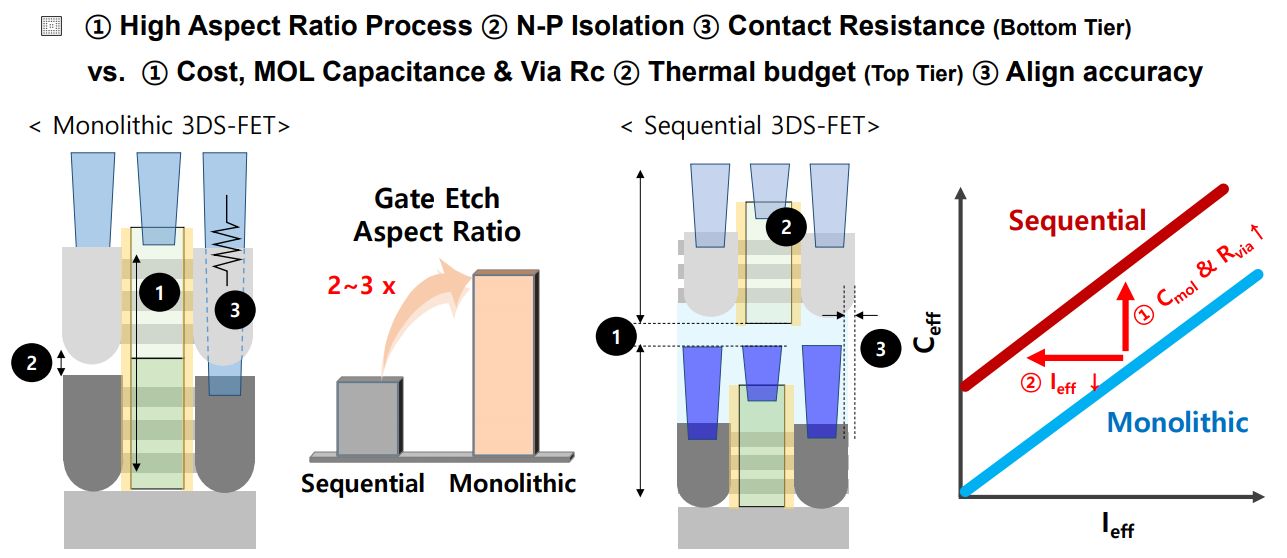

이러한 CFET을 구현할 수 있는 공정 방식은 크게 두가지로 나뉩니다. 먼저, 하나의 웨이퍼 위에서 순차적으로 NMOS, PMOS를 만들어가는 Monolithic 방식, 그리고 각각의 NMOS, PMOS를 따로 만들어 본딩을 하는 Sequential 방식이 있습니다.

| Monolithic 방식 | Sequential 방식 |

|---|---|

특징: 한 웨이퍼에서 상/하단 소자 순차 성장 장점 비용 효율성 : 단일 웨이퍼이기에 정밀제어 : Self-Aligend 소자 구현 가능 격리 : 좁은 N-P 분리 공간 확보 단점 High-AR 식각 난이도 높음 하단 MOSFET의 MOL 컨택 공정 어려움 수직 게이트 분리 어려움(가운데 절연층) |

특징: 두 소자 각각 웨이퍼에서 제작 후 본딩 장점 설계 유연성 : 상/하단 소자 아키텍쳐 독립 설계 가능 소재 또한 채널 물질 선택 자유 (Ge, 2D 등) 단점 상/하단 소자 간 정렬(Alignment) 난이도 극상 (1~2nm 오차) 높은 비용(웨이퍼 2장 사용 및 본딩 과정 추가) Thermal Budget 이슈 제약 |

현재 업계에서는 양산성 측면에서 Monolithic 방식에 무게를 두고 있다고 합니다. 특히 적층 순서(Stacking Order)는 Top NMOS / Bottom PMOS 구조가 선호되는데, 이는 하단 PMOS에 압축 응력(Compressive Stress)을 가하기 더 유리하여 성능 확보에 좋기 때문입니다.

Monolithic과 Sequential 공정 비교

3. 게임 체인저: Back Side Power Delivery Network (BSPDN)

3DS-FET (CFET)의 기술적 과제로는 수직 contact 및 N-P isolation, 앞선 공정방식에 따른 Thermal Budget과 Align 이슈 등이 있습니다. 3DS-FET은 구조와 공정이 정말 복잡해지기에 기존의 GAAFET보다 효율이 떨어 질 수 있습니다.

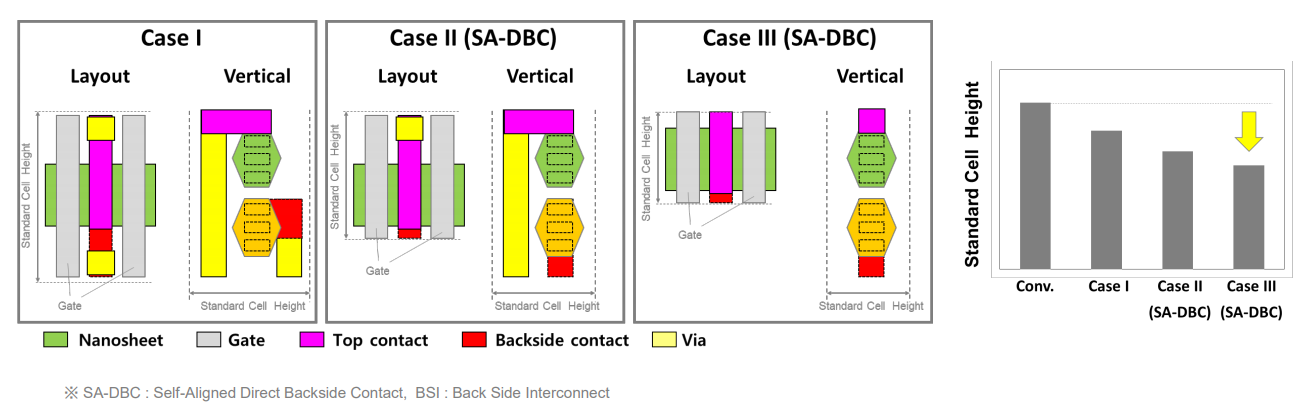

하지만 이런 3DS-FET의 잠재력을 폭발시키는 것은 후면 전력 공급(BSPDN) 기술입니다. 웨이퍼 뒷면에서 전력을 공급하여 신호 라인의 혼잡도를 낮춥니다. 강연에서는 특히 SA-DBC (Self-Aligned Direct Backside Contact) 기술이 강조되었습니다.

- 면적 축소: SA-DBC 기술 적용 시 Standard Cell Height 약 40% 감소

- SRAM 신뢰성: 기생 전류 경로 차단으로 125°C 고온에서 Hold Current 약 15.4% 감소

아무래도 BSPDN을 도입하면, 높이가 줄어들고, 또 위에서 단순히 컨택을 내렸을 경우 길어지는 도선들도 짧아지니 불필요한 부분에서 Para Capacity가 줄어들어 소자 성능도 향상되는 것 같습니다.

총평

이번 강연을 보며 느낀 점은, 무어의 법칙을 지속하기 위한 엔지니어들의 처절한 노력이 계속되고 있다는 점입니다. 소자 구조와 공정은 갈수록 외계의 기술이 되어가고 있는데, FinFET에서 GAA로, 그리고 3DS-FET으로 이어지는 과정은 Inner Spacer, Stress Engineering, BSPDN과 같은 요소 기술들이 극한으로 최적화되어야만 가능한 영역입니다.

10년 전 FinFET 도입 때의 우려를 딛고 성공했듯, 수많은 공정 난제를 뚫고 GAA와 CFET 또한 우리의 주력 기술이 될 것입니다.

Reference:

Based on "Limitation and Innovation of transistor technologies", M. Kang (Samsung Electronics), IEDM 2025 Short Course.

'반도체뉴스' 카테고리의 다른 글

| CES 2026 3대 메가트렌드 분석 및 반도체 산업 관점의 고찰(관련주, 기업) (0) | 2026.01.14 |

|---|---|

| 'K-패키징'의 굴기: 엔비디아 R&D 설립과 19조 청주 팹이 예고하는 미래 (0) | 2026.01.13 |

| 코스피 4,500 시대 개막과 SK하이닉스 HBM4 16단 최초 공개 (1) | 2026.01.07 |

| '12만전자·65만닉스' 시대 개막과 HBM4 기술 초격차 분석 (0) | 2025.12.31 |

| [심층리포트] 수출 7,000억 불 시대의 주역,K-반도체 슈퍼사이클 투자 전략 총정리 (1) | 2025.12.23 |