반도체의 고집적화로 여러 문제가 발생하며, 트렌지스터 또한 끊임없이 발전되었다.

그래서 MOSFET ➡ FINFET ➡ GAAFET으로 발전하며 유효 채널 길이가 길어지며 성능이 발전하였다.

이후에도 FORKSHEET NS FET , CFET 등의 신기술이 있긴 하지만 아직 보편화 되지는 않았다.

오늘은 GAAFET의 구조에 대해 자세히 이해하기 위해 공정 순서를 차근차근 알아볼 것이다.

1. 채널 형성을 위해 Si와 SiGe 박막을 반복적으로 증착.

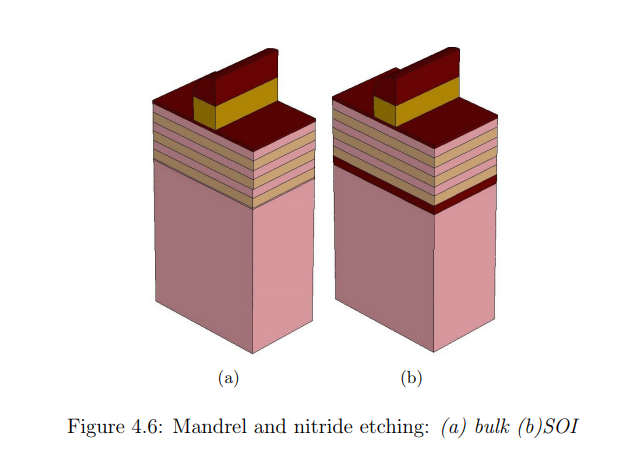

Mandrel : 패터닝 과정에서 sidewall spacer를 형성하기 위한 중심 기둥(mask 역할)입니다.

BULK 구조 : 채널 아래 절연층 없음. 실리콘이 기판 전부

SOI구조 : FBDI가 존재

- Top Si / Buried Oxide (BOX) / Handle Si로 구성.

- 채널 바로 아래에 절연체(BOX)가 있어:

- 기생 커패시턴스 감소

- DIBL 등 단채널 효과 감소

- 정확한 시트/채널 두께 제어 가능

- 열방출 불리

2. Fin Patterning & Vertical Etch

spacer 생성 ➡ mandrel 에칭 ➡ nitride 에칭 ➡ fin 형성

→ Nitride 마스크 폭이 nanosheet width 결정

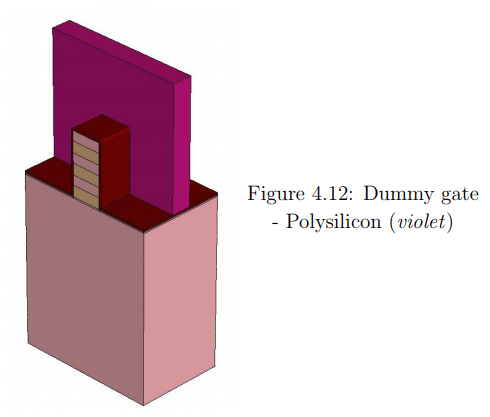

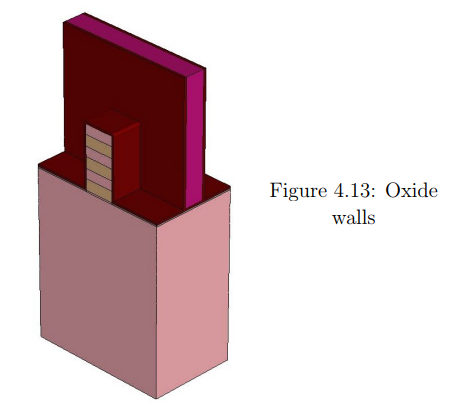

3. dummy gate 형성

oxide wall 필요성 : 이후 S/D 형성때 게이트 주변 채널 이온 침투 방지 and 스페이서 지지대(기준)

SICN 마스크 씌우고 dummy gate 밖에 튀어나온 SiO2 오버에칭 이후 Inner Spacer 형성

<Inner Spacer 공정>

4. S/D 형성

Silicidation :

소스/드레인 접촉부에 금속-실리콘 반응을 유도해 **저저항 금속실리사이드층(TiSi₂ 등)**형성

→접촉 저항(Rc) 최소화

더미게이트 제거

5. 게이트 형성

si : 채널

Ox : 계면 안정 Passivation

Hfo : 고유전체여서 얇은 막으로도 leakage 줄이고 전기장 강화, SS개선

1차 금속 : TiN : Barrier, metal/HfO₂ 안정화

2차 금속 : TaN : EWF 조절, 확산 방지

3차 금속 : TiAL :EWF 조정, 산소 스캐빈징 → 특히 n-type GAAFET에서 Vth 를 낮추기 위해 채택됨

- 산소 스캐빈징이란,metal gate stack 내 특정 금속이 산소를 빼앗아가는 현상으로,Si와 High-k 물질 사이의 SiO₂ 인터페이스 층(Interfacial Layer, IL)의 두께를 제어하거나 줄이는 기술

Gate Stack 형성의 중요성

- Threshold Voltage (Vth) 조절

- SS (Subthreshold Swing) 개선

- Gate leakage 및 reliability 개선

- EOT 최소화 → drive current (Ion) 극대화

이후 나머지 빈 부분은 cvd/ALD로 gap fill

6. contact

이후 Source / Drain / Gate에 각각 알맞은 Contact 연결

Etching을 알맞게 하는 기술이 중요.

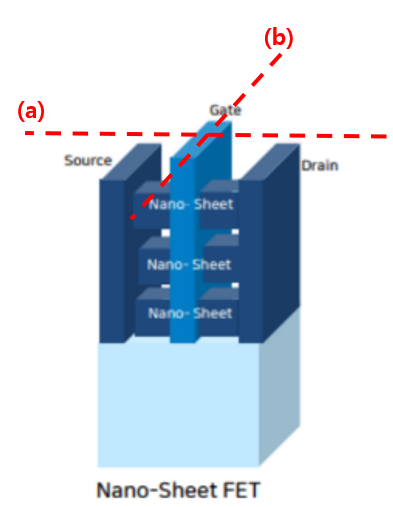

공정을 마친 후 단면은 다음과 같다(a,b로 각각 잘랐을 경우)

Reference

- From FinFET to Nanosheet Si-SiGe GAAFET: fabrication process simulation and analysis

- State of the art and Future Perspecitves in Advanced CMOS Technology

- A Review of the Gate-All-Around Nanosheet FET Process Opportunities

'반도체 공부 > 반도체 제품' 카테고리의 다른 글

| 차세대 메모리로의 FeFET, 강점, 동작원리 (0) | 2026.03.25 |

|---|---|

| GAAFET의 한계를 넘는 기술들, Forksheet과 BSPDN (0) | 2026.03.11 |

| [SRAM] 대표적인 메모리 소자인 SRAM 기본 구조 및 동작 이해하기 (0) | 2025.05.12 |

| 모바일 AP 제품(Application Processor, SOC, IP) (0) | 2025.04.02 |

| [PRAM] PRAM의 동작원리 (0) | 2024.11.26 |